#### **Research Article**

### Journal of Robotics and Automation Research

# A Novel Design of Heterojunction Double Ferroelectric MOSFET (HDF-MOSFET) with Steep Subthreshold Slope and High Ion/Ioff Current Ratio

Mojtaba Hosseinzadeh Sani 1\*, Parisa Sami², Mahsa Hassanianzabi³.

1School of Precision Instrument and Opto-electronics Engineering, Tianjin University, Tianjin, China

2Faculty of Electronic and Information Engineering, Xi'an Jiaotong University, Xi'an, China

3Faculty of New Sciences and Technologies, University of Tehran, Tehran, Iran

#### Corresponding author

Mojtaba Hosseinzadeh Sani, School of Precision Instrument and Optoelectronics Engineering, Tianjin University, Tianjin, China.

Submitted: 10 Aug 2022; Accepted: 16 Aug 2022: Published: 18 Aug 2022

Citation: Sani, M.H., Sami, P., Hassanianzabi, M. (2022). A Novel Design of Heterojunction Double Ferroelectric MOSFET (HDF-MOSFET) with Steep Subthreshold Slope and High Ion/Ioff Current Ratio. J Robot Auto Res, 3(2), 235-241.

#### Abstract

In this work, three novel structures using ferroelectric material are designed and simulated. The proposed structures are Improved Priority, Single Ferro (SF-MOSFET), Double Ferro (DF-MOSFET), and Heterojunction Double Ferro (HDF-MOSFET), respectively. Unlike other structures, these structures have a contact gate and two ferroelectric layers, and an insulation layer between these layers.  $HfO_2$  is used instead of the common perovskite ferroelectric layers such as zirconium lead titanate (PbZrTiO $_3$ ) and strontium bismuth tantalum (SrBi $_2$ Ta $_2$ O $_3$ ), which makes it compatible with the CMOS process as well as the scalability of the device. Ferroelectric layers, Insulation and Ferroelectric layers are stacked (F-I-F). Placing double ferro layers in the form of a stack increases the polarization effects and improves the application of the structure in memory. The memory performance can be saved even after the power is turned off and the readout properties are not destructive for double ferroelectric stack, perovskite Lead Zirconium Titan ate (PZT) is chosen as the ferroelectric materials. The DF-MOSFET structure, value of on-state current  $I_{ij} = 10^{-2}$ , off-state current  $I_{ij} = 10^{-15}$ , and memory Windows MW = 0.9V for memory applications. In the barrier layer of HDF-MOSFET structure, from composite materials that have used  $TiO_2 = 60\%$  and  $TiO_2 = 40\%$ , the amount of  $TiO_2 = 10-4.8$ ,  $TiO_2 = 10-35.2$  and  $TiO_3 = 10-4.8$ ,  $TiO_$

**Keywords:** SF-MOSFET, DF-MOSFET, HDF-MOSFET, I<sub>m</sub>/I<sub>off</sub> Ratio, Memory Windows (MW)

#### Introduction

Field effect transistors are a group of transistors in which the current is controlled by an electric field. Due to the fact that in these transistors only one type of charge carrier (free electron or hole) is involved in creating electric current, they can be considered as unipolar transistors as opposed to bipolar transistors (in which the majority and minority carriers simultaneously play a role). Are placed. Field effect transistors have source, drain and gate tripods [1]. These transistors are divided into two groups: MOSFET and Jift. In this type of transistors, unlike connecting bipolar transistors, which control the current of the emitter and collector with the input current to the base, the control of the source and drain current is done by applying voltage to the gate [2, 3].

Ferroelectric is a property in materials that causes permanent electric dipoles to form on the surface of a single cell due to the regular arrangement of atoms molecules, so that their direction can be adjusted by applying an external electric field. Ferroelectric is a nonlinear dielectric with properties such that a certain range is independent of permeability in the intensity of the applied electric field. Dielectric displacement is the sensing electric field applied using the hysteresis loop profile. The dielectric constant of these materials is very high independently and is in the threshold of 1000 to 10,000. The dielectric parameters specifically depend on the temperature and the ferroelectric properties and are only within the defined temperature range. Dielectric polarization occurs in the absence of an external electric field, and this polarization can

be coupled to apply an electric field. Scientists have developed a silicon oxide that could create a state of ferroelectricity to pave the way for the production of low-consumption, efficient electronic memory.

Ferroelectricity is a property by which materials can be electrically polarized. The polarity of the material can be rotated by applying an external electric field, which is used in long-term storage of data. In a research, the ferroelectric phenomenon and its properties are studied. Crystals with constant dipole moment are known as polar crystals. The permanent dipole moment is defined as M = eiri, where ri is the paraelectric distance ei from the origin and summation is performed on all the loads present in the single cell. Ferroelectric crystals are a special type of polar crystals in which the direction of spontaneous polarization can be reversed by applying an electric field. This switching is known and is associated with hysteresis. In most cases, these objects are similar to ferromagnetic bodies in which the direction of the magnet is reversed by changing the direction of the magnetic field, and this is the reason for choosing the name ferroelectric for these objects. Ferroelectrics are a subset of piezoelectric materials and have extensive properties such as high electrical polarization, strong piezoelectric capability, nonlinear optical activity, and remarkable nonlinear dielectric behavior. These features are used for various applications in electronic devices such as sensors, actuators, IR detectors, memories that are stored after a power outage [4 -10].

One of the major advantages of ferroelectric materials is their ability to be stored in memory. In fact, a ferroelectric material has spontaneous and reversible polarization, even in the part without electric field, and the memory program is based on the hysterical behavior of polarization with electric field [11-13]. The description curve of the first polarization of a ferroelectric device is called the first polarization curve. When an alternating electric field is applied to a ferroelectric, a hysterical behavior is created according to the intensity of the applied field. At zero field strength, there are two equally stable polarization modes, + Pr or -Pr, depending on the polarization time.

This behavior of ferroelectric materials allows the design of a binary device in the form of a ferroelectric capacitor with a metal-ferroelectric-metal structure that can be reversed. Either of these two modes can be encrypted as -0 or -1 in the computer memory, and is non-volatile, and even when the electric field is cut off, information is stored in the device because no electric field is required to maintain the state of the device. To change the status of the device, a threshold part (mandatory field) greater than + Ec or -Ec is required. A strong ferroelectric material has a high Pr value and a low Ec value. In order to determine a ferroelectric device, it is necessary to determine the waste behavior and the value of Pr. In addition, because ferroelectric materials have piezoelectricity, spontaneous polarization, and high dielectric constants, they are useful for numerous other applications due to the inherent anisotropy of dielectric properties. For example, the high nonlinear polarization of ferroelectric materials has made these devices promising for electrical and optical devices [14, 15].

To simulate the effects of polarization and hysteresis of ferroelectric materials, the ferroelectric model in the atlas in the simulation code must be used. This model can be activated by setting the "FERRO" parameter in the phrase "MODELS" [16]. Permissibility, used in the Poisson equation, is expressed in Equation (1) as follows:

$$\varepsilon(E) = ferro.epsp + \frac{ferro.ps}{2\delta}$$

$$\cdot sec h^2 \left[ \frac{E - ferro.ec}{2\delta} \right]$$

(1)

Where, E is the electric field, *ferro.epsf* is the allowable value of ferro.pr, the residual polarization is in  $C/cm^2$ , ferro.ps is spontaneous polarization in  $C/cm^2$  and ferro.ec is the forced field in V/cm.  $\delta$  can be expressed mathematically as Equation (2).

$$\delta = ferro. ec \left[ log \left[ \frac{1 + \frac{ferro. pr}{ferro. ps}}{1 - \frac{ferro. pr}{ferro. ps}} \right] \right]^{-1}$$

(2)

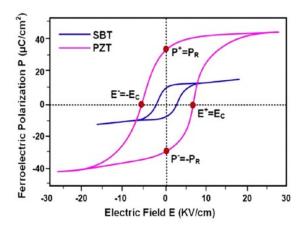

There are two main models of ferroelectric materials which are PZT and SBT, in this paper the PZT model is used. In principle, each of the above ferroelectric materials is suitable for memory applications and is also intended for applications by ferroelectric field (FeFETs). These two substances differ in the values of polarization and forced field [17]. Table 1 shows the parameters of these two materials and Figure 1 shows a comparison of the polarization behavior of these two ferroelectric materials.

**Figure 1:** The polarization hysteresis loops of the two main models of ferroelectric materials PZT and SBT.

Table 1: Comparison of Ferroelectric materials of PZT and SBT.

| Parameters | Unit   | PZT | SBT |

|------------|--------|-----|-----|

| PR         | μC/cm2 | 32  | 8   |

| PS         | μC/cm2 | 40  | 10  |

| EC         | KV/cm2 | 70  | 30  |

| Er         | -      | 250 | 250 |

In this paper, we integrate the ferroelectric material into a MOS-FET transistor, which has already been done by scientists. But a new work that has been done in this article is to introduce the new double ferroelectric MOSFET (DF-MOSFET) and Heterojunction double ferroelectric (HDF-MOSFET) method, which aims to improve memory applications, performance speed, sub-threshold slope, on and off current and off current. This proposed new method, in addition to being used in MOSFET transistors, can also be tested in TFET transistors and other field effect transistors.

#### **Proposed Devices**

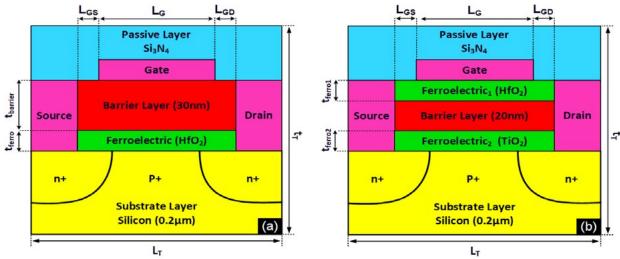

The proposed devices are designed and simulated in Figure 2 using Atlas section of the Silvaco software. In section (a), the structure

is designed with a channel length of L<sub>ch</sub> =20 nm and a single ferroelectric MOSFET (SF-MOSFET). Instead of the ferroelectric layer, material  $HfO_2$  with a thickness of  $t_{ferro} = 10$  nm has been used and the barrier layer has used oxide insulation with a thickness of  $t_{\text{barrier}} = 40 \text{ nm}$ . The substrate layer is made of silicon material with a thickness of 200 nm. Drain and source metals is made of Ti/Al/Ni/Au materials with thicknesses of 5/20/5/10 nm. The gate is also made of Mo/Au with thicknesses of 5/5 nm. The length of the Schottky gate is  $L_G = 60$  nm and the distance between the gate and the source is  $L_{\rm GD}$  = 10 nm. Also, the distance between gate and source is  $L_{\rm GS}$  = 10 nm. The total length of the device is  $L_{\rm T}$  = 100 nm and total thicknesses is  $t_T = 240$  nm. Figure 2 (b) shows the proposed double ferroelectric structure (DF-MOSFET), witch a ferro layer below the barrier layer and from TiO, material is used instead of Ferreroelectric. The thickness of this layer is  $t_{ferro2} = 10$ nm. The concentration of p+ doping in the channel layer is  $1\times10^{16}$ cm<sup>-3</sup> and the concentration of n+ doping is equal to or  $1\times10^{19}$  cm<sup>-3</sup>. The Si<sub>2</sub>N<sub>4</sub> material has been used as a passive layer on the device due to its high heat transfer.

Figure 2: Poroposed Device (a) Single ferroelectric (SF-MOSFET), (b) Double ferroelectric (DF-MOSFET).

The parameters used in the properties of ferroelectric material are ferro.epsf = 35, ferro.ps =  $4.9\times10^{-6}$  C/cm², ferro.pr =  $4.8\times10^{-6}$  C/cm² and ferro.ec =1.1×106 V/cm, respectively. Figure 2 Overvoltage (VGS-VTH, where VTH is the threshold voltage) Dependent drain current (I $_{\rm DS}$ ) for SF-MOSFET with L $_{\rm ch}$  = 20 nm channel length in V $_{\rm DS}$  = 1 V. In order to analyze and compare performance parameters much better, the sub-threshold slope was defined as the average slope between the off-state current and the threshold.

## Single Ferroelectric MOSFET (SF-MOSFET) I-V Curve of Single Ferroelectric Transistor (Linear & dB Scale)

As shown in Figure 2 (a), this structure used a ferroelectric layer that actually does the memory work and a Barrier layer (barrier below the gate metal) to transfer the field electric into the channel layer with length of  $L_{\rm C}=40{\rm nm}$  and a gate length of  $L_{\rm G}=60{\rm nm}$ . The Barrier layer material is made of HfO<sub>2</sub> and the bottom layer is made of  $S_{\rm i}O_{\rm 2}$ . As can be seen, the yellow area of the silicon is of type p+, that two n+ wells have been created in this area. When positive voltage is applied to the gate metal, the ferroelectric layer

does nothing, and in fact the barrier layer does its job and transfers the field electric to the channel layer. The ferroelectric layer has polarization properties that store electron and hole residues in itself. and this residue creates a window called Memory Window (MW). The smaller it is, the better for us. As shown in Figure 3, the transistor is turned off before the  $V_{th} = -1.8 \text{ V}$ , after this voltage ( $V_{th}$ ), the transistor starts to turn on. By increasing the voltage, we increase the current. We have the maximum current at V = 6V.

Figure 3: I-V curve of single ferroelectric transistor.

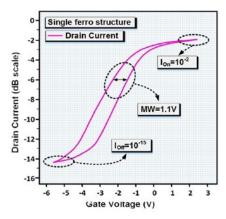

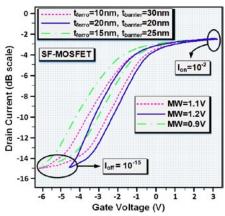

According to Figure 4 the amount of on current is  $I_{on} = 2^{-10}$  (dB scale) and the amount of off current is  $I_{off} = 10^{-15}$  (dB scale) and the amount of memory window is MW = 1.1V. According to the figure, with the gate voltage increasing from  $V_{G} = -6V$  to  $V_{G} = 3V$ , the amount of drain current is increasing and at the same time the electron and hole waste are collected in the ferroelectric layer. When we reduce the gate voltage, we see that the drain current decreases from another path, which the same difference in the return path creates a memory window.

Figure 4: I-V curve of single ferroelectric transistor (dB scale).

#### Effects of Thickness and Materials on SD-MOSFET

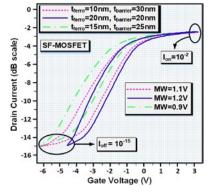

In this section (Figure 5), the effects of changing the thickness of the Barrier layer ( $t_{\rm barrier}$ ) and the ferroelectric layer ( $t_{\rm ferro}$ ) on the  $I_{\rm on}$ ,  $I_{\rm off}$  and MW parameters are investigated. As can be seen in the figure, with thickness changes, it has no effect on the  $I_{\rm on}$  and  $I_{\rm off}$  parameters. But there are changes in the Windows window that increase the thickness of the stored waste effects. From this figure we conclude that when the ferroelectric thickness is  $t_{\rm ferro} = 15$ nm, it has the best memory windows (MW=0.9V) state.

Figure 5: Effects of thickness changes on SF-MOSFET (dB scale).

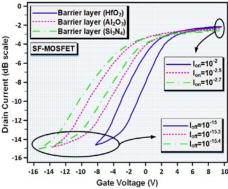

In addition, the effects of the materials type used in the barrier layer on the important parameters are investigated (Figure 7). Here we used three types of materials that have different physical properties and do not have problems in terms of stress and adhesion to barrier layers. The materials used in the barrier layer are HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and Si<sub>3</sub>N<sub>4</sub>. As shown in the figure 6, all parameters change with the change of the barrier layer material.

**Figure 6:** Effects of different materials changes on SF-MOSFET (dB scale).

#### **Double Ferroelectric MOSFET (DF-MOSFET)**

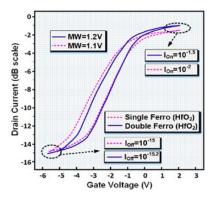

In the SF-MOSFET structure, the  $I_{on}/I_{off}$  current ratio increased slightly. In order to increase the  $I_{on}/I_{off}$  current ratio and decrease the amount of memory window, the DF-MOSFET structure is designed and presented. As can be seen in Figure (2b), in this structure, a double ferroelectric material is used, one under the gate and one under the barrier layer. A barrier layer material is  $HfO_2$ . In double collapse, the two layers of residue electrical are added together algebraically, so the amount of residue must be doubled. This causes the Ion current to increase and the Ioff current to decrease, resulting in a smaller memory window.

As shown in Figure 7, they are compared in an equal manner, in the double ferro structure the value of the memory window is reduced by 0.1V, the amount of on current is increased by  $I_{\rm on}=10^{-0.2}$ , and the amount of off current is reduced by  $I_{\rm off}=10^{-0.2}$ .

Figure 7: Comparison of single and double output structures.

#### **Effects of Materials and Thickness on DF-MOSFET**

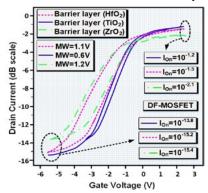

To determine the best material, the change of material in the barrier layer in the double ferro state is investigated. According to Figure 8, TiO<sub>2</sub> has the best performance compared to HfO<sub>2</sub> and ZrO<sub>2</sub>. These parameter improvements include on and off current and memory windows. The amount of on current in the case of the barrier layer is made of TiO<sub>2</sub> is 10<sup>-1.8</sup> amps and the amount of off current is 10<sup>-15.4</sup> and the amount of memory window is 0.6 V.

Figure 8: Effects of material changes on the DF-MOSFET structure

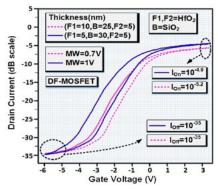

In this section, we want to investigate the effects of thicknesses of ferroelectric layers (F1, F2) and barrier layer (B) on the parameters of on and off current and memory windows. As can be seen in Figure 9, the thicknesses of the ferroelectric layer and the dam layer are investigated for the two states [(F1=10, B=25, F2=5) & (F1=5, B=30, F2=5)]. Here the ferroelectric material is HfO<sub>2</sub> and the dam material is SiO<sub>2</sub>. At first glance, we see that with changes in the thickness of F1, F2, and B layers, the off current has decreased significantly and has reached 10-35. It can be concluded that the leakage current in this type of structure has been very low, and that prevents power leakage losses. The value of the memory window for F1+F2 = 15nm, and B = 25nm is MW = 0.7V. And for F1+F2=10nm, B=30 memory window equal to MW = 1V. Therefore, as the total F1, F2 decreases and B increases, the amount of memory window decreases. The amount of current in the thickness state B> F2, F2 increases and its value is equal to  $I_{on} = 10^{-4.9}$ .

**Figure 9:** Effects of thickness changes on the DF-MOSFET structure.

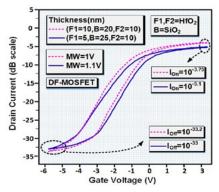

Figure 10 shows the others thicknesses of F1, F2 and B layer. As can be seen from the results of Figure 10, it can be concluded that the thicker the ferroelectric layer, the larger the memory window. On the other hand, the off current decreases and as a result the leakage current decreases.

**Figure 10:** Effects of thickness changes on the DF-MOSFET structure.

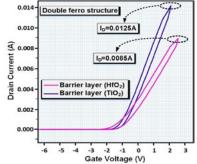

Next, we want to check the linear value of the on current for both  ${\rm HfO_2}$  and  ${\rm TiO_2}$  materials. As can be seen in Figure 11, it can be concluded that changes of up to one epsilon in the dB state cause large changes in the linear state. According to the material, material  ${\rm TiO_2}$  performs better than material  ${\rm HfO_2}$ , and the amount of light current when material  ${\rm TiO_2}$  is used in ferroelectric layers is equal to  ${\rm I_D} = 0.0125~{\rm A}$ .

**Figure 11:** Effects of material changes (HfO2, TiO2) on the DF-MOSFET structure.

### Heterojunction the Barrier Layer in DF-MOSFET (HDF-MOSFET)

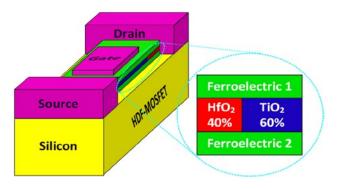

After the double ferroelectric idea, we briefly consider another idea. Next idea in addition to examining the effects on the thickness and type of material, we want to divide the barrier layer into two parts and use two different materials. With the transverse changes of the barrier layer, we calculate the values of different important parameters. Figure 12 also shows the best case of the proposed HDF-MOSFET, which is drawn in 3D to have a better understanding of the structure.

**Figure 12:** The final proposed heterojunction DF-MOSFET (HDF-MOSFET).

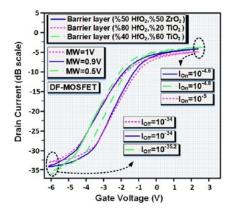

As can be seen in Figure 13, the barrier layer has been transformed into two equal parts in the form of heterojunction, and in one part material (HfO<sub>2</sub>=50%) and in the other part material (ZrO<sub>2</sub>=50%). In this case, the amount of on-state current is  $I_{on}=10^{-4.8}$  and the amount of off-state current is  $I_{on}=10^{-34}$  and the memory window is equal to MW = 0.9 V. The ratio of on-state current to off-state current is equal to  $I_{on}/I_{off}=1.584\times10^{29}$ . In the next case, the barrier layer has been transformed into two unequal parts (HfO<sub>2</sub>=80% and TiO<sub>2</sub>=20%) in the form of heterojunction, and in one part material HfO<sub>2</sub> and in the other part material TiO<sub>2</sub> is placed. In this case, the amount of on-state current is  $I_{off}=10^{-34}$  and the memory window is equal to MW = 1 V. The ratio of on-state current to off-state current is equal to  $I_{on}/I_{off}=1\times10^{29}$ .

Finally, the barrier layer has been transformed into two unequal parts (TiO $_2$ =40% and TiO $_2$ =60%) in the form of heterogeneity, and in one part material HfO $_2$  and in the other part material TiO $_2$ . In this case, the amount of on current is  $I_{\rm on}=10^{-4.8}$ , the amount of off current is  $I_{\rm off}=10^{-35.2}$  and the memory window is equal to MW=0.5 V. The ratio of on-off-state current is equal to  $I_{\rm on}/I_{\rm off}=2.5\times10^{30}$ .

**Figure 13:** Effects of transverse changes of two-part barrier layer and different materials on important parameters of DF-MOSFET structure.

According to the obtained results, it can be concluded that when 40% of the barrier layer is made of material  $\mathrm{HfO}_2$  and 60% of material  $\mathrm{TiO}_2$  is used, it is the best case that the ratio of on-off current reaches its maximum value of  $\mathrm{I}_{\mathrm{on}}/\mathrm{I}_{\mathrm{off}} = 2.51 \times 10^{30}$ . Finally, we want to present the process of improving the MOSFET structure using ferroelectric material in the form of a table. Table 2 shows a comparison of important structure parameters such as  $\mathrm{I}_{\mathrm{on}}$ ,  $\mathrm{I}_{\mathrm{off}}$ , on/off current ratio, and MW for SF-MOSFET, DF-MOSFET, and HDF-MOSFET structures.

Table 2: Measurement of important parameters in the proposed structures

| Proposed   | Materi-<br>als          | I <sub>on</sub> (A/μm²) | I <sub>off</sub> (A/μm²) | MW(V) | $I_{\rm on}/I_{\rm off}$ |

|------------|-------------------------|-------------------------|--------------------------|-------|--------------------------|

| SF-MOSFET  | $HfO_2$                 | 10-2                    | 10-15                    | 1.1   | 1×10 <sup>13</sup>       |

| DF-MOSFET  | HfO <sub>2</sub>        | 10-1.5                  | 10-15.2                  | 0.9   | 5.01×10 <sup>13</sup>    |

| HDF-MOSFET | HfO <sub>2</sub> & TiO2 | 10-4.8                  | 10-35.2                  | 0.5   | 2.51×10 <sup>30</sup>    |

#### Conclusion

In the MOSFET structure, the important parameters are  $I_{on}$  and  $I_{off}$ ,  $I_{on}/I_{off}$  ratio and memory window (MW). To have an ideal structure, we need to increase the amount of  $I_{on}$  current and decrease the amount of  $I_{off}$  current and the memory window. The higher the  $I_{on}/I_{off}$  ratio, the performance structure is better. In this paper, we designed and proposed three new structures, in each of which an improvement in the structural parameters was observed. Among the proposed structures, the best HDF-MOSFET structure was introduced, which has an extremely low Ioff current and minimizes leakage losses ( $10^{-35.2}$ ). On the other hand, the  $I_{on}/I_{off}$  current ratio increased significantly and reached  $2.51 \times 10^{30}$ . Finally, the memory window value was reduced to 0.5V. In general, the proposed structure is very suitable for memory applications and work at high power and frequency.

#### **Declarations**

#### Availability of data and material

The authors have no competing interests.

#### **Funding**

This paper is not financially supported by any organizations or institutions.

#### Reference

- Tarr, N. G., Walkey, D. J., Rowlandson, M. B., Hewitt, S. B., & MacElwee, T. W. (1995). Short-channel effects on MOS-FET subthreshold swing. Solid-state electronics, 38(3), 697-701.

- Roy, K., Mukhopadhyay, S., & Mahmoodi-Meimand, H. (2003). Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proceedings of the IEEE, 91(2), 305-327.

- Algueró, M., Gregg, J. M., & Mitoseriu, L. (Eds.). (2016). Nanoscale Ferroelectrics and Multiferroics: Key Processing and Characterization Issues, and Nanoscale Effects, 2 Volumes (Vol. 1). John Wiley & Sons.

- 4. Pardo, L., & Ricote, J. (Eds.). (2011). Multifunctional polycrystalline ferroelectric materials: processing and properties (Vol. 140). Springer Science & Business Media.

- 5. Meyerson, B. (2004). (IBM) Semico Conf.

- Li, Y., Lian, Y., Yao, K., & Samudra, G. S. (2015). Evaluation and optimization of short channel ferroelectric MOSFET for low power circuit application with BSIM4 and Landau theory. Solid-State Electronics, 114, 17-22.

- Aziz, A., Breyer, E. T., Chen, A., Chen, X., Datta, S., Gupta, S. K., Yin, X. (2018, March). Computing with ferroelectric FETs: Devices, models, systems, and applications. In 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE) (pp. 1289-1298). IEEE.

- 8. Hueting, R. J. (2018). The balancing act in ferroelectric transistors: How hard can it be?. Micromachines, 9(11), 582.

- Han, Q., Tromm, T. C., Hoffmann, M., Aleksa, P., Schroeder, U., Schubert, J., ... & Zhao, Q. T. (2018). Subthreshold behavior of floating-gate MOSFETs with ferroelectric capacitors. IEEE transactions on electron devices, 65(10), 4641-4645.

- Yamaguchi, M., Gotow, T., Takenaka, M., & Takagi, S. (2019). Drive current enhancement of Si MOSFETs by using anti-ferroelectric gate insulators. Japanese Journal of Applied Physics, 58(SB), SBBA15.

- 11. Pešić, M., Schroeder, U., & Mikolajick, T. (2019). Ferroelectric one transistor/one capacitor memory cell. In Ferroelectricity in Doped Hafnium Oxide: Materials, Properties and Devices (pp. 413-424). Woodhead Publishing.

- 12. Mueller, J., Slesazeck, S., & Mikolajick, T. (2019). Ferroelectric field effect transistor. In Ferroelectricity in Doped Hafnium Oxide: Materials, Properties and Devices (pp. 451-471). Woodhead Publishing.

- Fengler, F., Park, M. H., Schenk, T., Pešić, M., & Schroeder, U. (2019). Field cycling behavior of ferroelectric HfO2-based capacitors. In Ferroelectricity in Doped Hafnium Oxide: Materials, Properties and Devices (pp. 381-398). Woodhead Publishing.

- Yan, H., Inam, F., Viola, G., Ning, H., Zhang, H., Jiang, Q., ... & Reece, M. J. (2011). The contribution of electrical conductivity, dielectric permittivity and domain switching in ferroelectric hysteresis loops. Journal of Advanced Dielectrics, 1(01), 107-118.

- Mikolajick, T., Müller, S., Schenk, T., Yurchuk, E., Slesazeck, S., Schröder, U., ... & Müller, J. (2014). Doped hafnium oxide–an enabler for ferroelectric field effect transistors. Advances in Science and Technology, 95, 136-145.

- Wu, Y. F., Keller, B. P., Fini, P., Keller, S., Jenkins, T. J., Kehias, L. T., ... & Mishra, U. K. (1998). High Al-content AlGaN/GaN MODFETs for ultrahigh performance. IEEE Electron Device Letters, 19(2), 50-53.

- Wang, J., Li, A., Xu, S., Song, C., Geng, Y., Ye, L., ... & Xu, W. (2019). Solvation-Enhanced Intermolecular Charge Transfer Interaction in Organic Cocrystals: Enlarged C–C Surface Close Contact in Mixed Packing between PTZ and TCNB. ACS omega, 4(6), 10424-10430.

**Copyright:** ©2022: Mojtaba Hosseinzadeh Sani. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.